기술동향

반도체 패키징 기술 동향 개요

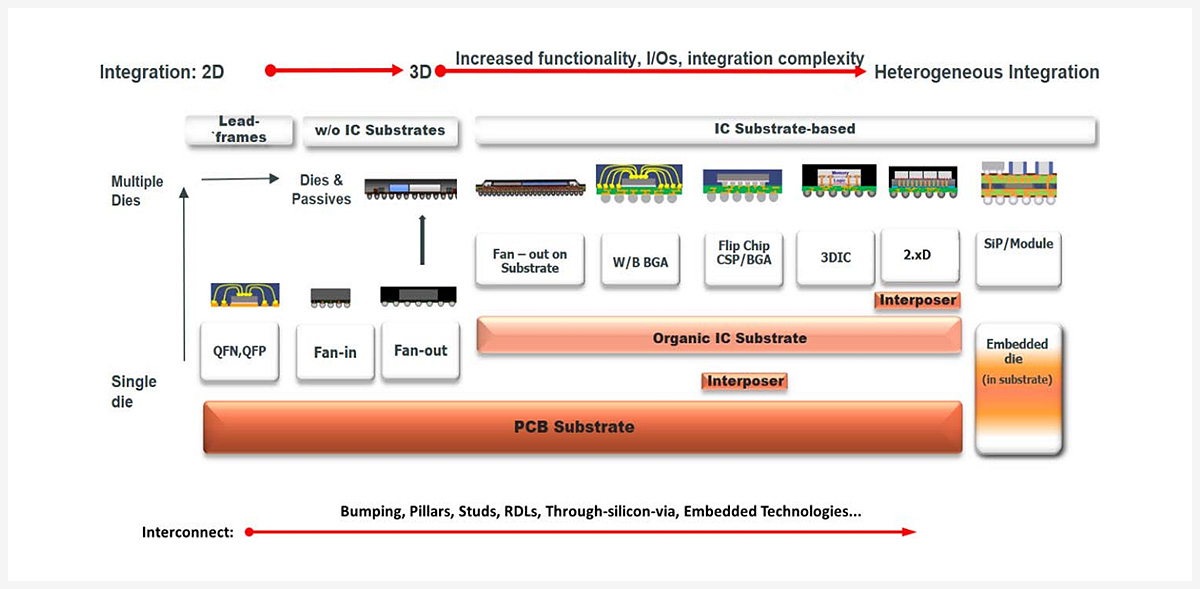

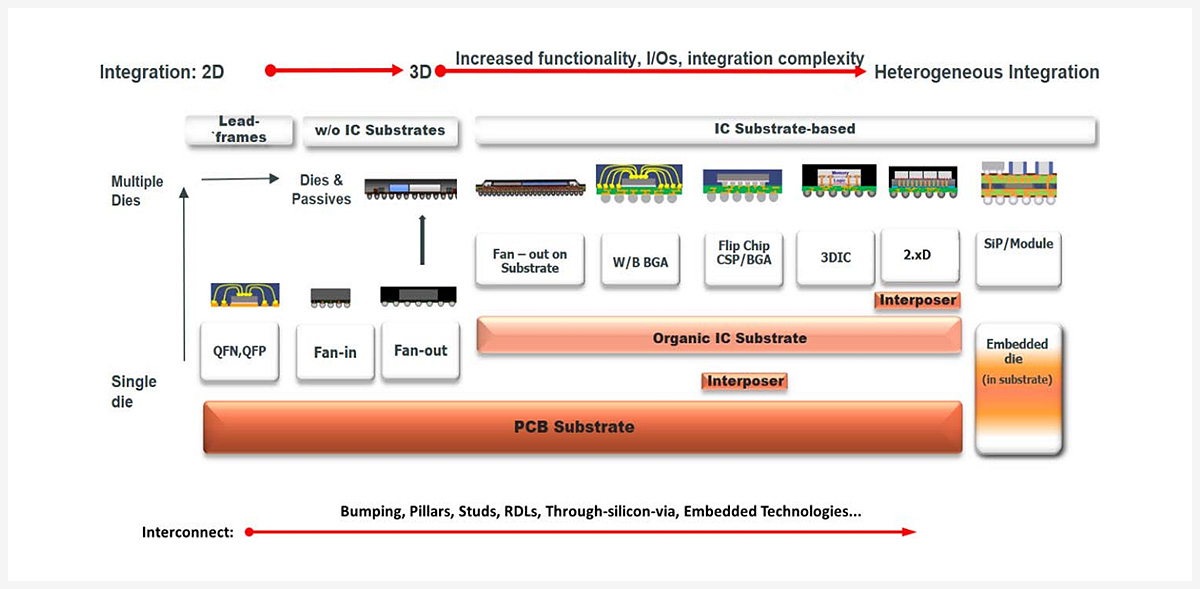

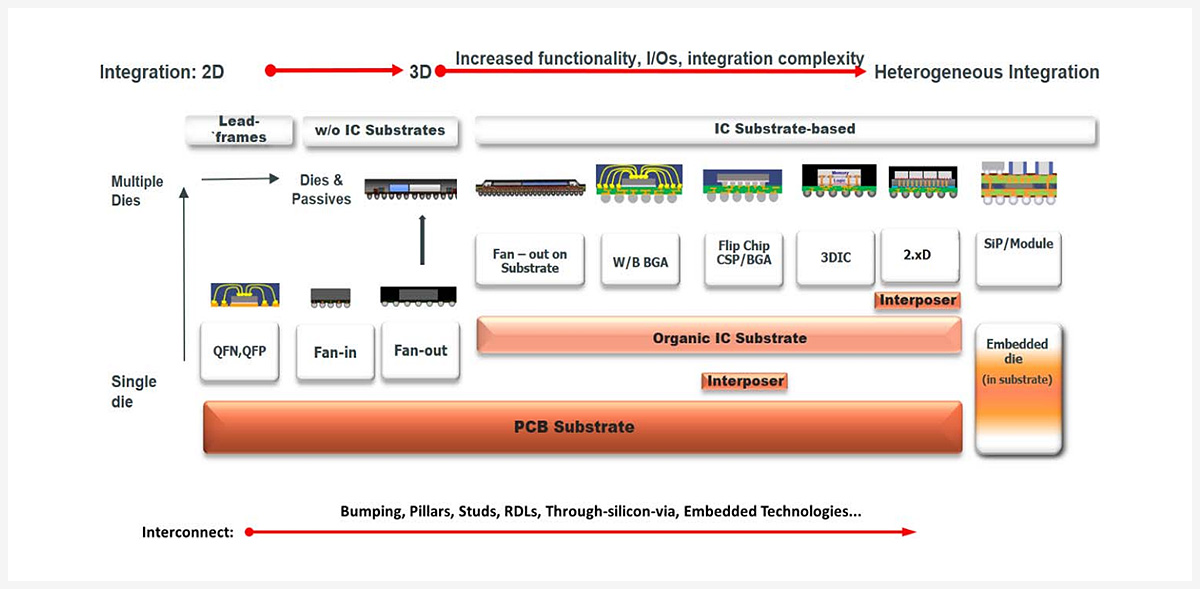

패키징 기술은 개별 반도체 회로(Integrated circuit, IC) 단위에서 다수의 IC와 수동소자를 집적한 모듈 형태의 패키징 기술로 진화

- 패키징 공정은 전통적인 리드프레임 계열의 방식인 QFN, TSOP 등에서 솔더볼・범프 등을 이용하는 BGA, FC 등 기술을 거쳐 고집적・다기능 소자 구현이 가능한 FO-WLP, TSV 등 첨단 패키징 기술로 패러다임 변화

- 이와 같은 첨단 패키징 기술은 내장 부품의 수율과 시스템 전체에 대한 높은 이해도가 요구되는 기술집약적 산업으로 신속한 시장 수요 파악 및 경제적 대응 역량 필요

- 최근, 더 많은 부품이 하나의 패키지로 구현함에 따라 시스템적인 성격을 나타내기 시작 했으며, 패키지 기판(모듈기판)의 성장률이 전통적인 기판보다 높아지는 추세

- 전통적인 리드프레임에서 PCB 및 SMT(Surface mount technology) 기반으로 진화 해온 패키징 기술은 범핑, 인터커넥션, 적층(Stacking) 및 재배선(Redistribution layer, RDL) 등 전(前)공정 기술의 도입을 통한 차세대 기술로 발전 중

- 수 ~ 수십 nm 레벨의 IC와 수 μm 크기의 패키지 기판 크기 격차를 해소하기 위해 패키지 내부 연결 배선에 반도체 공정을 도입하거나, 단일 패키지에 많은 외부 소자를 내장하여 외부로 나오는 단자 수를 줄이는 등의 시도 중

- 특히, 전공정을 이용한 IC 간 미세연결(Interconnection)은 전송손실 및 기생성분을 최소화 하여, 고속 대용량 데이터 전송과 높은 동작 주파수 대역에서의 발생하는 기술적인 문제해결

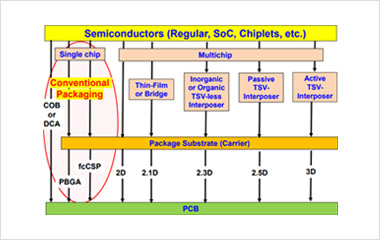

- 파운드리와 OSAT기업을 중심으로 기존 FC(Flip-Chip) 등과 같은 패키징 기술을 비롯하여 2.5D/3D 적층을 위한 TSV 기술, Fan-Out WLP(FOWLP) 기술 등 첨단 패키징 기술에 대한 비중 증가

- 이처럼 단순 반도체의 보호 및 연결 기능에 그쳤던 기존의 반도체 패키징의 역할은 시스템 레벨 집접화(System-level integration)의 방향으로 진화 중이며 궁극적으로 2.5D/3D 적층 방식으로 발전 중

- 프로세서, 메모리, 센서, 광, RF 및 MEMS와 같이 다양한 기능의 소자들을 통합하기 위해 기존의 솔더링이나 와이어 본딩이 아닌 RDL공정 등을 사용하여 회로 간 미세연결(interconnection) 구조를 구현

- 전술한 바와 같이 전공정의 기술적・경제적 한계 봉착에 따라 패키지 안에서 로직, 메모리, 및 다양한 칩을 이종접합하기 위한 다양한 패키징 기술들3)이 개발

- HI 패키지 구현을 위해서는 SiP, WLP 및 다양한 2D/2.5D/3D 배선 기술(TSV 기술 등)과 같은 배선 통로를 확장할 수 있는 고난이도 기술 필요

반도체 패키징 기술 로드맵

1965년 최초의 반도체 패키지가 발명된 이후 반도체 패키징 기술은 비약적으로 발전했으며 수천 가지의 다양한 반도체 패키지 유형이 만들어졌다. 아래 차트는 반도체 패키징의 역사를 보여준다.

특히 반도체 패키징의 두 가지 주요 추세인 높은 핀 수 해결과 작은 풋프린트 요구 사항 수용을 보여준다.

오늘날 대부분의 반도체 장치는 다이와 연결 와이어의 손상을 방지하기 위해 패키지로 둘러싸여 있다. 그러나 ASIC 엔지니어나 구매 관리자에게 묻는다면 반도체 패키징은 실리콘 다이에 바람직하지 않은

추가 요소이다. 총 칩 면적이 증가하고 총 비용이 증가하며 실리콘 다이의 전기적 성능이 감소한다. 그러나 반도체 패키징에는 상당한 이점도 있다.

반도체 패키지는 실리콘 다이와 PCB 사이의 전기적 연결을 가능하게 한다. 이 패키지는 고밀도 다이 패드를 더 넓은 영역으로 확장하여 PCB 레이아웃 및 어셈블리를 쉽게 만들 수 있도록 도와준다.

전력 소모가 많은 애플리케이션에서 반도체 패키지의 책임은 실리콘 다이에서 생성된 열을 방열판과 같은 넓은 표면으로 분산키는 것이다. 이를 통해 다이는 고온 환경에서 정상적으로 계속 작동할 수 있다.

-

3D (Flip Chip and Wirebond) Packaging

-

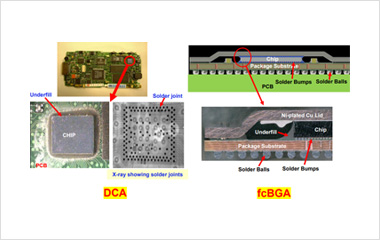

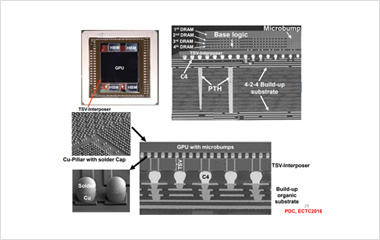

Conventional Packaging: Direct Chip Attach (DCA) and Flip Chip Ball Grid Array (fcBGA)

-

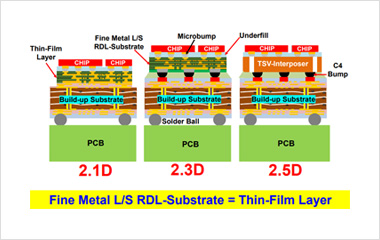

2.1D, 2.3D, and 2.5D IC Integration

-

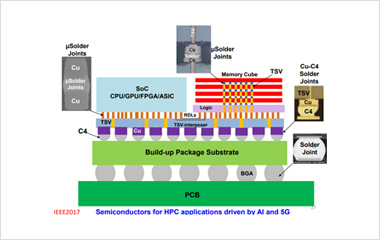

2.5D IC Integration

-

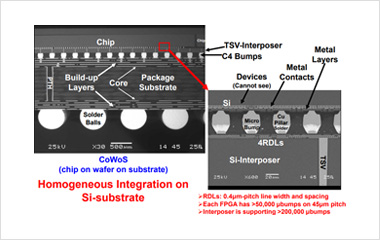

Xilinx/TSMC’s 2.5D IC Integration with FPGA

-

2.1D, 2.3D, and 2.5D IC Integration

-

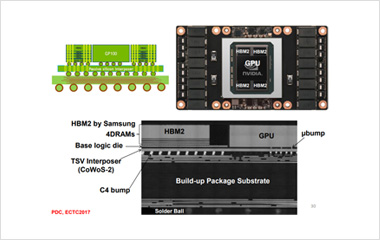

NVidia’s P100 with TSMC’s CoWoS-2 and Samsung’s HBM2

-

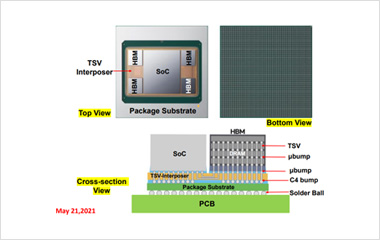

Samsung’s Interposer-Cube4 (I-Cube4) (2.5D IC Integration)

-

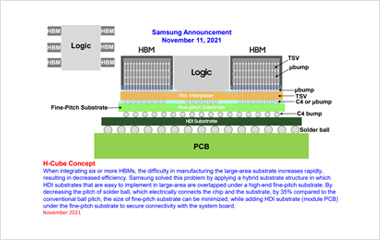

2.5D Integration Hybrid Substrate Cube(H-Cube) Solution for High Performance Applications

-

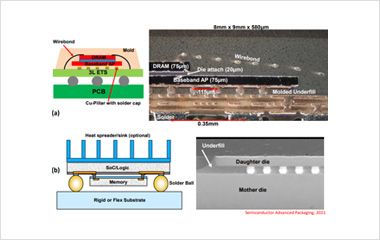

3D (Flip Chip and Wirebond) Packaging

-

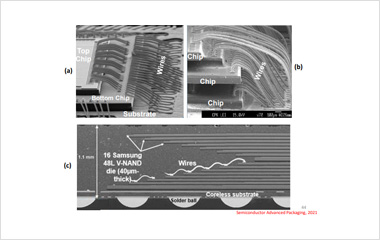

3D (Wirebnonding) IC Packaging

-

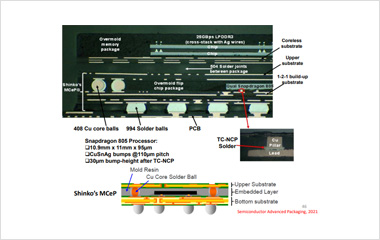

3D (PoP with flip chip) IC Packaging (Qualcomm)

-

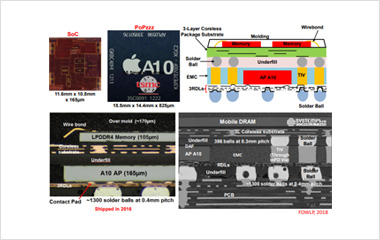

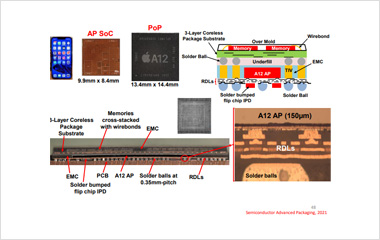

3D PoP : Appla/TSMC InFO (Integrated fan Out) fot the iPhone Applacion Processor (Chip-First Die Face-up)

-

3D (PoP with Fan-Out) Packaging (Apple/TSMC)

-

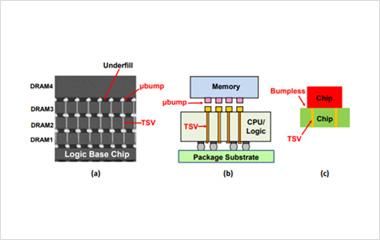

3D IC Integration

-

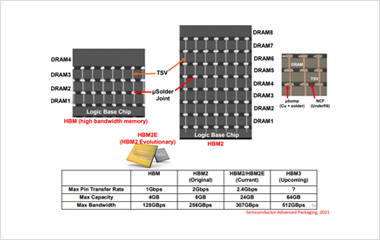

3D IC Integration with Active Interposer (High Bandwith Memory)

-

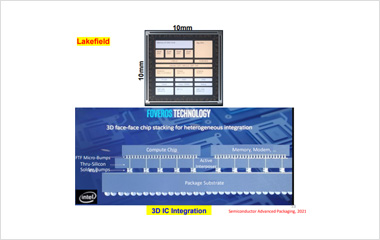

Intel 3D IC Integration-FOVEROS Technology

-

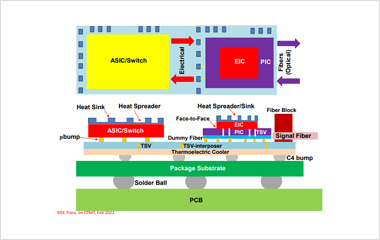

3D Heterogeneous Integration of EIC and PIC Devices

출처

- KISTEP 한국과학기술기획평가원 기술동향브리프 2020-16호 반도체 후공정(패키징) https://anysilicon.com/semiconductor-packaging-history-trends/

- https://news.skhynix.com/light-thin-short-and-small-the-development-of-semiconductor-packages/

- Heterogeneous Integration Roadmap, 2021 Edition (http://eps.ieee.org)

- John H Lau, Unimicron Technology Corporation, Recent Advances and Trends in Advanced Packaging, IEEE EPS Binghamton Chapter, April 13, 2022